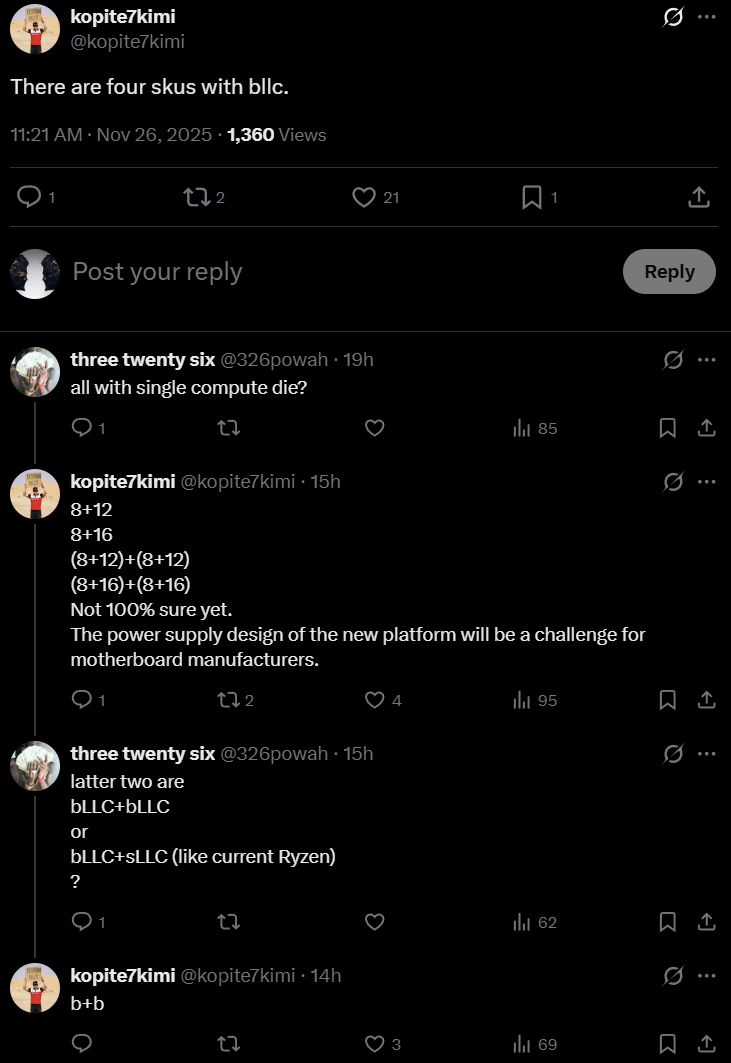

隨著 AMD 大緩存的 X3D 處理器在遊戲性能上取得巨大成功,Intel 明顯正準備在其下一代 Nova Lake-S 桌面 CPU 上採取策略進行反擊。最新消息指出,Nova Lake-S 系列中至少將有四款型號會配備 bLLC(Big Last-Level Cache,大型末級緩存)的配置。 根據 Kopite7kimi 的消息,這些擁有超大緩存的 Nova Lake-S CPU 都將是“不鎖頻”的設計,旨在提供最佳性能和超頻潛力,具體型號如下:

其中,雙 Compute Tile 型號包含兩個 8P+16E 核心 Tile,提供 48 個核心,加上額外的 4 個低功耗(LPE)核心,總核心數達到 52 個。每個 Compute Tile 將配備 144MB 的 bLLC 緩存,使總緩存容量高達 288MB。 除了 52 核版本的旗艦,雙 Tile 系列還將包括一個基於兩個 8P+12E Tile 的 40 核版本(總計 44 核),預計也將配備 288MB 的 bLLC 緩存。

單 Compute Tile 型號則分別為 8P+16E(總計 28 核)和 8P+12E(總計 24 核)配置,均將配備 144MB 的 bLLC 緩存,通常情況下,Intel 可能會率先推出這些單 Tile 版本。 Kopite7kimi 還表示,超大緩存的引入將對主板商構成挑戰,他們需要在下一代 LGA 1954 接口的主板上設計出更先進的供電方案,以滿足這些高性能、高緩存 CPU 的需求。如此龐大的緩存,顯然是 Intel 針對 AMD 的雙 3D 緩存 CCD 設計的回擊,AMD 預計將首次推出雙 3D V-Cache 型號,首款預計為銳龍 9 9950X3D2。

Nova Lake-S 型號規格

| 型號 | 核心數 | bLLC 緩存 |

|---|---|---|

| 2x 8+16 | 48 核 + 4 LPE 核 | 288MB |

| 2x 8+12 | 40 核 + 4 LPE 核 | 288MB |

| 8+16 | 24 核 + 4 LPE 核 | 144MB |

| 8+12 | 20 核 + 4 LPE 核 | 144MB |

單 Compute Tile 型號則分別為 8P+16E(總計 28 核)和 8P+12E(總計 24 核)配置,均將配備 144MB 的 bLLC 緩存,通常情況下,Intel 可能會率先推出這些單 Tile 版本。 Kopite7kimi 還表示,超大緩存的引入將對主板商構成挑戰,他們需要在下一代 LGA 1954 接口的主板上設計出更先進的供電方案,以滿足這些高性能、高緩存 CPU 的需求。如此龐大的緩存,顯然是 Intel 針對 AMD 的雙 3D 緩存 CCD 設計的回擊,AMD 預計將首次推出雙 3D V-Cache 型號,首款預計為銳龍 9 9950X3D2。